1. Tujuan [kembali]

a. Mempelajari tipe tipe MOSFET

b. Mempelajari karakteristik MOSFET

2. Alat dan Bahan [kembali]

1. MOSFET type IRF530

MOSFET (Metal Oxide Semiconductor Field Effect Transistor) adalah sebuah perangkat semionduktor yang secara luas di gunakan sebagai switch dan sebagai penguat sinyal pada perangkat elektronik. MOSFET adalah inti dari sebuah IC ( integrated Circuit ) yang di desain dan di fabrikasi dengan single chip karena ukurannya yang sangat kecil. MOSFET memiliki empat gerbang terminal antara lain adalah Source (S), Gate (G), Drain (D) dan Body(B).

MOSFET bekerja secara elektonik memvariasikan sepanjang jalur pembawa muatan ( electron atau hole ). Muatan listrik masuk melalui Saluran pada Source dan keluar melalui Drain. Lebar Saluran di kendalikan oleh tegangan pada electrode yang di sebut dengan Gate atau gerbang yang terletak antara Source dan Drain. ini terisolasi dari saluran di dekat lapisan oksida logam yang sangat tipis. Kapasitas MOS pada komponen ini adalah bagian Utama nya.

2. Resistor

Resistor adalah komponen dasar elektronika yang umumnya digunakan pada rangkaian elektronika ataupun rangkaian listrik lainnya dengan fungsi utama yaitu menghambat/membatasi jumlah arus input atau arus yang mengalir masuk ke dalam satu rangkaian, dimana kemampuan resistor dalam membatasi arus masuk sesuai dengan spesifikasi resistor tersebut. Sesuai dengan namanya resistor bersifat resistif dan umumnya terbuat dari bahan karbon.

Bahan Resistansi Pada Resistor

Berikut ini beberapa bahan yang paling umum digunakan dalam pembuatan resistor

1. Komposisi Karbon

Memiliki daya rendah hingga menengah, toleransi dan satbilitas yang dihasilkan dari resistor komposis karbon relatif buruk, disamping itu juga menghasilkan lebih banyak noise dibanding tipe resistor lainnya.

2. Film Karbon

Memiliki daya rendah, toleransi serta stabilitas yang dihasilkan lumayan bagus, serta tidak menghasilkan banyak noise.

3. Film Metal

Memiliki daya rendah hingga menengah, toleransi serta stabilitas yang dihasilkan dari ressitor jenis ini sangat baik, disamping itu hampir tidak ada noise yang dihasilkan.

3. Kapasitor

Kapasitor atau kondensator oleh ditemukan oleh Michael Faraday (1791-1867) pada hakikatnya adalah suatu alat yang dapat menyimpan energi/ muatan listrik di dalam medan listrik, dengan cara mengumpulkan ketidakseimbangan internal dari muatan listrik atau komponen listrik yang mampu menyimpan muatan listrik yang dibentuk oleh permukaan (piringan atau kepingan) yang berhubungan yang dipisahkan oleh suatu penyekat.

Ketika kapasitor dihubungkan pada sebuah sumber tegangan maka piringan atau kepingan terisi elektron. Bila elektron berpisah dari satu plat ke plat lain maka muatan elektron akan terdapat diantara kedua kepingan. Muatan ini disebabkan oleh muatan positif pada plat yang kehilangan elektron dan muatan negatif pada plat yang memperoleh elektron.

Kapasitor adalah komponen elektronika yang mempunyai kemampuan menyimpan elektron-elektron selama waktu yang tertentu atau komponen elektronika yang digunakan untuk menyimpan muatan listrik yang terdiri dari dua konduktor dan di pisahkan oleh bahan penyekat (bahan dielektrik) tiap konduktor di sebut keping.

3. Dasar Teori [kembali]

5.7 MOSFET JENIS DEPLESI

Seperti disebutkan dalam sub-chapter introduction, ada dua jenis FET: JFET dan MOSFET. MOSFET selanjutnya dipecah menjadi tipe penipisan dan tipe peningkatan. Istilah deplesi dan peningkatan menentukan mode operasi dasar mereka, sedangkan label MOSFET adalah singkatan dari metal-oxide-semiconductor-field-effect transistor (transistor efek medan-oksida-logam-semikonduktor). Sejak terdapat perbedaan karakteristik dan pengoperasian masing-masing jenis MOSFET, mereka tercakup dalam bagian terpisah. Pada bagian ini kita memeriksa tipe deplesi MOSFET, yang kebetulan memiliki karakteristik yang mirip dengan JFET di antaranya cutoff dan saturation di IDSS tetapi kemudian memiliki fitur karakteristik tambahan yang meluas ke wilayah polaritas yang berlawanan untuk VGS

Konstruksi Dasar

Konstruksi dasar MOSFET tipe deplesi saluran-n disediakan pada Gambar 5.23.

Alasan label metal-oksida-semikonduktor FET yaitu logam untuk saluran pembuangan, sumber, dan koneksi gerbang ke permukaan yang tepat — khususnya, terminal gerbang dan kontrol yang akan ditawarkan oleh luas permukaan kontak, oksida untuk lapisan isolasi silikon dioksida, dan semikonduktor untuk basa struktur tempat wilayah tipe-n dan p tersebar. Lapisan isolasi antara gerbang dan saluran telah menghasilkan nama lain untuk perangkat tersebut: FET gerbang terisolasi atau IGFET, meskipun label ini semakin jarang digunakan dalam literatur saat ini.

Operasi dan Karakteristik Dasar

Pada Gambar 5.24 tegangan gerbang-ke-sumber diatur ke nol volt dengan hubungan langsung dari satu terminal ke terminal lainnya, dan tegangan VDS diterapkan di drain-to-source terminal. Hasilnya adalah daya tarik potensial positif yang di buang secara electron bebas dari saluran-n dan arus yang serupa dengan yang dibentuk melalui saluran JFET. Faktanya, arus yang dihasilkan dengan VGS = 0 V terus diberi label IDSS, seperti yang ditunjukkan pada Gambar 5.25.

Pada Gambar 5.26, VGS telah disetel pada tegangan negatif seperti -1 V. Negatif potensial di gerbang akan cenderung menekan elektron menuju substrat tipe-p (seperti muatan menolak) dan menarik lubang dari substrat tipe-p (muatan berlawanan menarik) sebagai ditunjukkan pada Gambar 5.26. Bergantung pada besarnya bias negatif yang ditetapkan oleh VGS, tingkat rekombinasi antara elektron dan lubang akan terjadi yang akan berkurang jumlah elektron bebas dalam saluran-n yang tersedia untuk konduksi. Semakin negatif biasnya, semakin tinggi laju rekombinasi. Oleh karena itu, tingkat arus drain yang dihasilkan berkurang dengan meningkatnya bias negatif untuk VGS seperti yang ditunjukkan pada Gambar 5.25 untuk VGS = -1 V, -2 V, dan seterusnya, ke level pinch-off -6 V. Tingkat arus drain yang dihasilkan dan plot dari kurva transfer berjalan persis seperti yang dijelaskan untuk JFET.

p-Channel Deplesion-Type MOSFET

Konstruksi MOSFET

tipe-deplesi saluran-p persis kebalikan dari itu muncul pada Gambar 5.23.

Artinya, sekarang ada substrat tipe-n dan kanal tipe-p, seperti yang

ditunjukkan pada Gambar 5.28a. Terminal tetap seperti yang teridentifikasi,

tetapi semua polaritas tegangan dan arah arus dibalik, seperti yang ditunjukkan

pada gambar yang sama. drain karakteristik akan muncul persis seperti pada

Gambar 5.25 tetapi dengan VDS memiliki nilai negatif, ID memiliki nilai positif

seperti yang ditunjukkan (karena arah yang ditentukan sekarang dibalik), dan

VGS memiliki polaritas yang berlawanan seperti yang ditunjukkan pada Gambar

5.28c. Pembalikan di VGS akan menghasilkan gambar cermin (tentang sumbu ID)

untuk karakteristik transfer seperti yang ditunjukkan pada Gambar 5.28b. Dengan

kata lain, arus drain akan meningkat dari cutoff pada VGS VP di wilayah VGS

positif ke IDSS dan kemudian terus meningkat untuk nilai VGS yang semakin

negatif.

Simbol, Lembar Spesifikasi, dan Kasus Konstruksi

Simbol grafis

untuk MOSFET tipe deplesi saluran-n dan p disediakan pada Gambar 5.29.

Perangkat yang muncul pada Gambar 5.30 memiliki tiga terminal, dengan identifikasi terminal muncul pada gambar yang sama. Lembar spesifikasi untuk MOSFET tipe deplesi mirip dengan JFET. Tingkat VP dan IDSS disediakan bersama dengan daftar nilai maksimum dan karakteristik "on" dan "off" yang khas. Selain itu, bagaimanapun, karena ID dapat melampaui level IDSS, titik lain biasanya disediakan yang mencerminkan nilai ID khas untuk beberapa tegangan positif (untuk perangkat saluran-n). Untuk unit Gambar 5.30, ID ditentukan sebagai ID (on) = 9 mA dc, dengan VDS = 10 V dan VGS = 3,5 V

5.8 MOSFET TIPE PENINGKATAN

Meskipun ada beberapa kesamaan dalam konstruksi dan mode operasi antara MOSFET tipe deplesi dan tipe peningkatan, karakteristik MOSFET tipe peningkatan sangat berbeda dari apa pun yang diperoleh sejauh ini. Kurva transfer tidak ditentukan oleh persamaan Shockley, dan arus drain sekarang terputus sampai tegangan gerbang-ke-sumber mencapai besaran tertentu. Secara khusus, kontrol arus dalam perangkat saluran-n sekarang dipengaruhi oleh tegangan gerbang-ke-sumber positif daripada rentang tegangan negatif yang ditemui untuk JFET saluran-n dan MOSFET tipe-saluran-n deplesi.

Kontruksi dasar

Konstruksi dasar dari MOSFET tipe peningkatan saluran-n disediakan pada Gambar 5.31.

Lembaran bahan tipe-p dibentuk dari basis silikon dan lagi-lagi disebut sebagai substrat. Seperti halnya MOSFET tipe penipisan, media terkadang terhubung secara internal ke terminal sumber, sementara dalam kasus lain kabel keempat disediakan untuk kontrol eksternal pada level potensinya. Terminal sumber dan saluran kembali dihubungkan melalui kontak logam ke daerah n-doped, tetapi perhatikan pada Gambar 5.31 tidak adanya saluran antara dua daerah n-doped. Ini adalah perbedaan utama antara konstruksi MOSFET tipe deplesi dan tipe peningkatan — tidak adanya saluran sebagai komponen yang dibuat dari perangkat. Lapisan SiO2 masih ada untuk mengisolasi platform logam gerbang dari wilayah antara drain dan sumber, tetapi sekarang hanya dipisahkan dari bagian material tipe-p. Singkatnya, oleh karena itu, konstruksi MOSFET tipe peningkatan sangat mirip dengan MOSFET tipe deplesi, kecuali tidak adanya saluran antara drain dan terminal sumber.

Operasi dan Karakteristik Dasar

Jika VGS diatur pada 0 V dan tegangan diterapkan antara saluran dan sumber perangkat pada Gambar 5.31, tidak adanya saluran-n (dengan jumlah pembawa bebas yang banyak) akan menghasilkan arus efektif nol ampere— cukup berbeda dengan deplesi-type MOSFET dan JFET dimana IDSS=ID. Tidaklah cukup untuk memiliki akumulasi pembawa (elektron) yang besar di drain dan source (karena daerah n-doped) jika jalur gagal ada di antara keduanya. Dengan VDS beberapa tegangan positif, VGS pada 0 V, dan terminal SS langsung terhubung ke sumber, sebenarnya ada dua persimpangan p-n bias balik antara daerah n-doped dan substrat p untuk melawan aliran signifikan antara drain dan sumber.

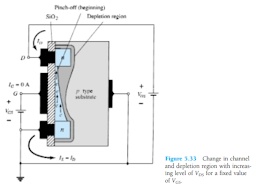

Karena VGS ditingkatkan melebihi ambang batas, kepadatan pembawa bebas di saluran yang diinduksi akan meningkat, menghasilkan peningkatan tingkat arus drain. Namun, jika kita mempertahankan VGS konstan dan meningkatkan level VDS, arus drain pada akhirnya akan mencapai level saturasi seperti yang terjadi untuk JFET dan MOSFET tipe deplesi. Leveling off ID disebabkan oleh proses pinching-off yang digambarkan oleh saluran yang lebih sempit di ujung drain dari saluran induksi seperti yang ditunjukkan pada Gambar. 5.33. Menerapkan hukum tegangan Kirchhoff ke tegangan terminal MOSFET dari Gambar 5.33, kami menemukan bahwa :

Jika VGS dipertahankan tetap pada beberapa nilai seperti 8 V dan VDS dinaikkan dari 2 menjadi 5 V, tegangan VDG [oleh Persamaan. (5.11)] akan turun dari -6 ke -3 V dan gerbang akan menjadi semakin kurang positif sehubungan dengan saluran pembuangan. Penurunan tegangan gate-to-drain ini pada gilirannya akan mengurangi gaya tarik pembawa bebas (elektron) di wilayah saluran induksi ini, menyebabkan pengurangan lebar saluran efektif. Akhirnya, saluran akan dikurangi ke titik pinch-off dan kondisi saturasi akan ditetapkan seperti yang dijelaskan sebelumnya untuk JFET dan MOSFET tipe deplesi. Dengan kata lain, peningkatan lebih lanjut dalam VDS pada nilai tetap VGS tidak akan mempengaruhi tingkat kejenuhan ID sampai kondisi kerusakan ditemui.

Karakteristik

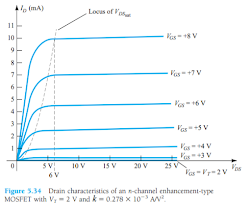

drainase Gambar 5.34 menunjukkan bahwa untuk perangkat Gambar 5.33 dengan VGS =

8 V, saturasi terjadi pada level VDS = 6 V. Faktanya, level saturasi untuk VDS

terkait dengan level VGS yang diterapkan oleh :

Untuk karakteristik Gambar 5.33, level VT

adalah 2 V, yang ditunjukkan oleh fakta bahwa arus drain telah turun menjadi 0

mA. Oleh karena itu secara umum:

Untuk nilai VGS kurang dari level ambang, arus drain dari MOSFET tipe peningkatan adalah 0 mA.

Gambar 5.34 dengan jelas mengungkapkan bahwa ketika tingkat VGS meningkat dari VT ke 8 V, tingkat kejenuhan yang dihasilkan untuk ID juga meningkat dari level 0 hingga 10 mA. Selain itu, cukup terlihat bahwa jarak antara tingkat VGS meningkat seiring meningkatnya VGS, sehingga kenaikan kenaikan arus pembuangan yang terus meningkat. Untuk tingkat VGS VT, arus pembuangan terkait dengan tegangan gerbang-ke-sumber yang diterapkan oleh hubungan nonlinear berikut:

ID=k(VGSVT)2 (5.13)

Sekali lagi, ini adalah istilah kuadrat yang menghasilkan hubungan nonlinear (melengkung) antara ID dan VGS. Istilah k adalah konstanta yang merupakan fungsi dari pembangunan perangkat. Nilai k dapat ditentukan dari persamaan berikut [berasal dari Eq. (5.13)] di mana ID (on)dan VGS (on) adalah nilai untuk masing-masing pada titik tertentu pada karakteristik perangkat:

K= Id(on)/(Vgs

(on)-Vt)2 (5.14)

substitusi ID(on)=10 mA ketika VGS

(on)=8 V dari karakteristik dari gambar 5.34

K= 10mA/(8V-2V)2=

10mA/36v2= 0,278x 10-3 A/V2

dan persamaan umum

untuk ID untuk karakteristik hasil Gbr. 5.34 dalam:

Id=0,278x 10-3 A/V2 Substitusi VGS= 4V,

Kita dapat: Id=0,278x 10-3 (4V-2V)2=1.11mA

sebagaimana diverifikasi oleh Gbr. 5.34. Di VGS = VT, istilah kuadrat adalah 0 dan ID = 0 mA atau analisis dc mosfets tipe peningkatan untuk muncul di Bab 6, karakteristik transfer akan kembali menjadi karakteristik yang akan digunakan dalam solusi grafis. Dalam Gbr. 5.35 karakteristik saluran pembuangan dan transfer telah ditetapkan berdampingan untuk menggambarkan proses transfer dari satu ke yang lain. Pada dasarnya, ini berlanjut seperti yang diperkenalkan sebelumnya untuk JFET dan MOSFETs tipe penipisan. Namun, dalam hal ini, harus diingat bahwa arus drain adalah 0 mA untuk VGS ≤ VT. Pada titik ini arus terukur akan menghasilkan ID dan akan meningkat seperti yang didefinisikan oleh Eq. (5.13). Perhatikan bahwa dalam mendefinisikan titik-titik pada karakteristik transfer dari karakteristik saluran pembuangan, hanya tingkat kejenuhan yang digunakan, sehingga membatasi wilayah operasi ke tingkat VDS lebih besar dari tingkat kejenuhan seperti yang didefinisikan oleh Eq. (5.12).

Kurva transfer gambar. 5.35 tentu sangat

berbeda dengan yang diperoleh sebelumnya. Untuk perangkat n-channel (induced),

sekarang benar-benar berada di wilayah VGS positif dan tidak naik sampai VGSVT.

Pertanyaannya sekarang muncul tentang cara memplot karakteristik transfer

mengingat tingkat k dan VT seperti yang disertakan di bawah ini untuk MOSFET

tertentu:

ID = 0,5x10-3 (VGS-4 V)2

Pertama, garis

horizontal digambar pada ID0 mA dari VGS0 V ke VGS4 V seperti yang ditunjukkan

pada Gbr. 5.36a. Selanjutnya, tingkat VGS yang lebih besar dari VT seperti 5 V

dipilih dan diganti menjadi Eq. (5.13) untuk menentukan tingkat id yang

dihasilkan sebagai berikut:

ID = 0,5x10-3 (VGS-4 V)2 ID = 0,5mA.

dan titik pada plot diperoleh seperti yang ditunjukkan pada gambar 5.36b. Level tambahan dari VGS dipilih dan level ID yang dihasilkan diperoleh. Khususnya, pada VGS= 6,7 dan 8V, level ID adalah 2, 4,5 dan 8 mA. masing-masing, seperti yang ditunjukkan pada plot yang dihasilkan pada Gambar 5.36c

p-Channel Enhancement-Type MOSFETs

Konstruksi MOSFET tipe peningkatan

saluran-p persis kebalikan dari yang tampak pada Gambar 5.31, seperti yang

ditunjukkan pada Gambar 5.37a. Artinya, sekarang ada substrat tipe-n dan daerah

p-doped di bawah saluran pembuangan dan sambungan sumber. Terminal tetap

seperti yang teridentifikasi, tetapi semua polaritas tegangan dan arah arus

dibalik. Karakteristik drain akan terlihat seperti yang ditunjukkan pada Gambar

5.37c, dengan peningkatan arus akibat nilai VGS yang semakin negatif.

Karakteristik transfer akan menjadi bayangan cermin (sekitar IDaxis) dari kurva

transfer Gambar.5.35, dengan ID meningkat dengan nilai VGS yang semakin negatif

di luar VT, seperti yang ditunjukkan pada Gambar 5.37b. Persamaan (5.11) sampai

(5.14) sama-sama berlaku untuk perangkat saluran-p.

Simbol, Lembar Spesifikasi, dan Konstruksi Kasus

Simbol grafis untuk MOSFET tipe peningkatan n-dan p-channel disediakan sebagai Gbr. 5.38. Sekali lagi perhatikan bagaimana simbol mencoba mencerminkan konstruksi perangkat yang sebenarnya. Garis putus-putus antara saluran pembuangan dan sumber dipilih untuk mencerminkan fakta bahwa saluran tidak ada di antara keduanya dalam kondisi tanpa bias. Ini, pada kenyataannya, satu-satunya perbedaan antara simbol untuk tipe deplesi dan MOSFETs tipe peningkatan.

Lembar spesifikasi untuk MoSFET tipe peningkatan n-channel Motorola disediakan sebagai Gbr. 5.39. Konstruksi kasus dan identifikasi terminal disediakan di sebelah peringkat maksimum, yang sekarang termasuk arus drain maksimum 30 mA dc. Lembar spesifikasi menyediakan tingkat IDSS di bawah kondisi "off", yang sekarang hanya 10 nA dc (di VDS = 10 V dan VGS = 0 V) dibandingkan dengan rentang ampere mili untuk JFET dan MOSFET tipe penipisan. Tegangan ambang batas ditentukan sebagai VGS(Th)dan memiliki kisaran 1 hingga 5 V dc, tergantung pada unit yang digunakan. Daripada menyediakan rentang kin Eq. (5.13), tingkat ID (on) khas (3 mA dalam hal ini) ditentukan pada tingkat VGS tertentu (on)(10 V untuk tingkat ID yang ditentukan). Dengan kata lain, ketika VGS =10 V, ID = 3 mA. Tingkat VGS (Th) yang diberikan, ID (on), dan VGS (on)mengizinkan penentuan k dari Eq. (5.14) dan penulisan persamaan umum untuk karakteristik transfer. Persyaratan penanganan MOSFETs ditinjau dalam Bagian 5.9.

Example 5.3

1. Buat sketsa karakteristik transfer untuk MOSFET tipe deplesi saluran dengan

IDSS 10 mA dan VP 4 V.

Solusi :

At VGS = 0 V, ID = IDSS = 10 mA

VGS = VP = -4 V, ID = 0 mA

VGS = VP/2 = -4 V/2 = -2 V, ID = IDSS/4 = 10 mA/4 = 2.5 mA

Dan pada ID = IDSS/2, VGS = 0.3VP = 0.3(-4 V) = -1.2 V

semuanya muncul pada Gambar 5.27.

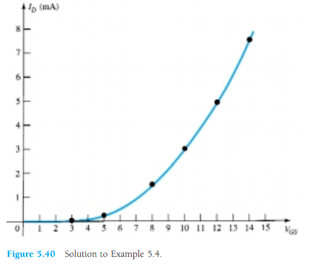

Example 5.4

1. Menggunakan data yang digunakan pada

lembar spesifikasi Gbr. 5.39 dan tegangan ambang batas rata-rata VGS (Th) = 3V

tentukan:

a. Nilai yang dihasilkan K untuk MOSFETs.

b. Karakteristik Transfer.

Tidak ada komentar:

Posting Komentar