1. Jurnal [Back]

2. Alat dan Bahan [Back]

a. IC 74LS112 (JK filp flop)

b. Power DC

c. Switch (SW-SPDT)

SPDT adalah singkatan dari Single Pole Double Throw. Switch jenis ini dapat menghubungkan dan memutuskan satu sambungan arus listrik pada dua arah sambungan.

d. Logicprobe

Logic Probe digunakan sebagai output

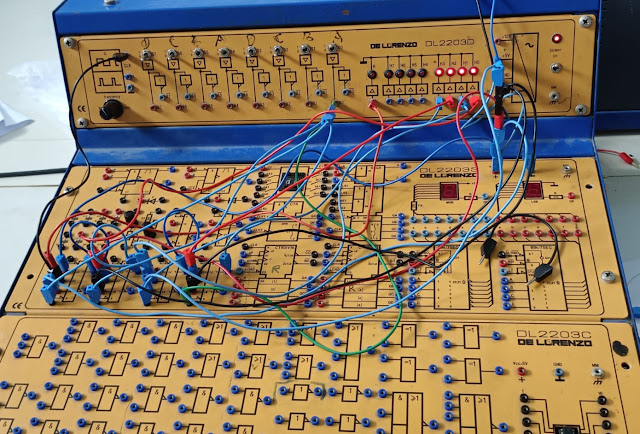

3. Rangkaian Simulasi [Back]

4. Prinsip Kerja Rangkaian [Back]

Rangkaian ini merupakan rangkaian counter asynchronous yang mana memiliki output 4 bit yang artinya ada 4 flip flop. Masing-masing flip flop mewakili 1 bit. Terdapat sinyal clock yang dihubungkan pada kaki CLK. Sesuai prinsipnya, counter asycroous ini disebut juga dengan counter serial yang mana flip flop dihubungkan secara seri dengan sinyal clock. Hal ini akan mengakibatkan flip flop akan aktif satu persatu secara bergantian dan sinyal clock akan mengalir dari flip flop yang satu ke yang lainnya. Sehingga output pada logic probenya akan aktif secara bergantian.

SPDT sebagai pengganti dari clock untuk memudahkan saat melihat perubahan pada output. Rangkaian ini merupakan jenis rangkaian falltime, dimana ia akan aktif ketika diberikan input berlogika 0. Pada percobaan, ketika diberikan input berlogika 0 maka output pada probe H0 akan berogika 1, sedangkan pada output H1,H2, dan H3 berlogika 0 sehingga membentuk urutan biner 1000. Hal ini terjadi karena input pada flip - flop menunggu output dari flip-flop sebelumnya sehingga output yang keluar delay sesuai dengan prinsip kerja counter asyncronous

5. Video Rangkaian [Back]

6. Analisa [Back]

1. Analisa output percobaan berdasarkan IC yang digunakan ?

JK Flip-Flop outputnya ada 8 bit sehingga digunakan 8 buah Flip Flop yang mana masing masingnya mewakili 1 bit. Dikarenakan IC yang digunakan dipasang secara seri dengan sumber sinyal clock maka sinyal clock akan mengalir dari IC yang paling ujung terlebuh dahulu. Hal ini mengakibatkan outputnya akan aktif secara bergantian / tidak serempak. Input yang masuk ke IC ada di kaki R dan S dengan berlogika 1 melewati gerbang NOT sehingga di dalam IC logikanya menjadi 0. Logika pada output akan bergantung dari pengaruh oleh sinyal clock

2. Analisa sinyal output yang dikeluarkan JK flip flop kedua dan ketiga

Output yang dikeluarkan oleh JK flip flop kedua mendapat sinyal input dari output Q JK flip flop kesatu. Ketika output JK flip flop kesatu bernilai 1 maka nantinya menjadi input dari JK flip flop kedua dan berlogika 0 selanjutnya menjadi input untuk kaki flip flop ketiga dan seterusnya. Logika melewatu gerbang NOT sehingga logika output pada JK flip flop ketiga akan berlogika 1

7. Link Download[Back]

Tidak ada komentar:

Posting Komentar